etorix

Members-

Posts

21 -

Joined

-

Last visited

-

Days Won

2

etorix last won the day on April 4 2025

etorix had the most liked content!

Recent Profile Visitors

The recent visitors block is disabled and is not being shown to other users.

etorix's Achievements

Junior Member (1/3)

12

Reputation

-

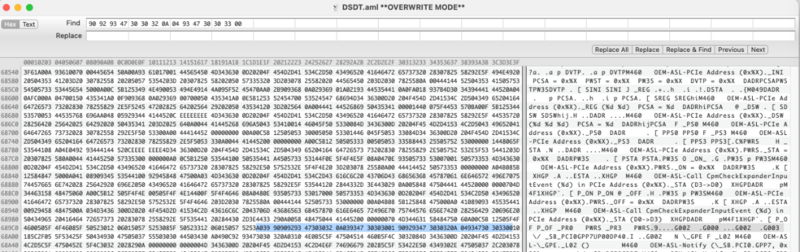

Thanks. The DSDT is confusing, with many conditions I havent seen with other manufacturers. If you see IOService:/AppleACPIPlatformExpert/PCI0@0/AppleACPIPCI/GPP7@2,1/IOPP/UP00@0/IOPP/DP40@8/IOPP/UP00@0/IOPP/DP28@5/IOPP/ethernet@0 \_SB.PCI0.GPP7.UP00.DP40.UP00.DP28 are all created as they should, despite the conditional declarations. But the NIC has no proper ACPI name ("ethernet@0"). Maybe a SSDT to name it would help? The scopes which matter are those where devices are declared. \_SB.PCI0.GPP7.UP00 is created under If (((G002 != 0x03) && (G000 != Zero))) at line 25080. This is patch #1a. \_SB.PCI0.GPP7.UP00.DP40.UP00 is created under If ((((G002 != 0x03) && (G000 == One)) && ( (G002 != 0x04) && (G003 != Zero)))) at lines 38352-38353. I do not think this is the issue, since you see the IOService path, but if I wanted to make a patch I would look for it in the binary DSDT.aml. Here it is (I looked for the OpCode sequence G002 != 0x04 && G003 != Zero, there is only one in the DSDT): The complete condition is: A0399090 92934730 30320A03 93473030 30019092 93473030 320A0493 47303033 00 where 'A0' is 'If'. Replace all bytes by 'A3' (NoOp) to remove the condition: A3A3A3A3 A3A3A3A3 A3A3A3A3 A3A3A3A3 A3A3A3A3 A3A3A3A3 A3A3A3A3 A3A3A3A3 A3 To make it more generic, make a mask for the padding byte '39' between 'A0' ('If') and test '90' ('&&'): FF00FFFF FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF FF SSDT-RTL8125.aml.zip

-

From the thread on AMD OSX, your board is a MSI X670e Gaming Plus Wifi, and the NIC is a Realtek 8125BG. Is this particular model supported under macOS? The three statements which are patched control many different devices. Do you know the path to the RTL8125BG?

-

Is this a MSI motherboard, by any chance? We know now that the actual ACPI is that some devices are created conditionally, and macOS does not like that; rather than manually editing the DSDT, the preferred solution is to use OpenCore to patch just the conditional declarations. Corpnews makes board-specific paches on request. I have tried to work out "universal" patches, but it seems that at least two versions will still be needed. Here is what should should work for you: am5_patches_msi.plist.zip

-

Which is a Thunderbolt device, right? HOW are you trying to get it to work? A (flashed) GC-Titan Ridge AIC should work. A Thunderbolt 4 AIC might be workable, though likely without hot plug. On-board USB4 from what appears to be an ASM4242 is a lost cause.

-

You're not bothering. A short analysis of your DSDT suggests that my set of generalised AM5 patches would work with this motherboard as well, so you're welcome to try and report if we can add your X670 Hero to the above ROG Strix B650E-F. To explain a bit: There are some padding bytes between If() (opcode: A0) and the conditions (opcodes: 90 and 9232 for && and !=). The content of these bytes can vary from board to board, but as long as the DSDT is not massively rewritten so as to change the number of padding bytes (here two), it's possible to set a mask and have "universal" patches. With a hex editor one can look for the core parts of the patches (excluding the A00000 part at the beginning): #1: 90 92934730 30320A03 93473030 3001 #2: 90 92934730 30320A03 90934730 30300192 93473030 340C2210 FA43 #3: 90 92934730 30320A03 93473030 300A02 There should be a single occurence of each of #2 and #3 in the whole DSDT.aml and a single occurence of #1 that is preceded by A0xxxx (A0 and TWO bytes), plus a few occurences of #1 preceded by A0xxxxxx (THREE bytes, thus not patched.) am5_patches.plist.zip

-

I see the same conditions as in just every AM5 DSDT that was posted here, and every set of patches provided by CorpNews. Here is a generic version of these three patches which should do for your motherboard… and many others, I hope. am5_patches.plist.zip

-

@sdmkx Have you tried the OpenCore patches from @corpghost, which @fabiosun has reposted multiple times in this thread? If it works, it is a much better way to do it—and if it doesn't work, we'll investigate why.

-

@Jaidy Maybe open a dedicated thread and post your EFI and SysReport from the WRX90 system?

- 284 replies

-

- amd vanilla patches

- amd kernel patches

- (and 2 more)

-

or even non-Pro. But 2 DIMMs per channels, so reduced speed (and probably best to keep to the RAM QVL). In the event that either of you had a free week-end to tinker while the WRX90 machine is at rest, you might give a try at hackintoshing it (with hyper-threading disabled for the 7985WX, and a compatible AMD GPU). It should not be that different from a TRX50.

- 284 replies

-

- amd vanilla patches

- amd kernel patches

- (and 2 more)

-

And, if I'm not mistaken, no one has ever hacked EPYC (3000/5000/7000/8000/9000, not 4000, which I would expect to be a given). On the Intel side of things, it seems that X299 "had quite a few people", but looks like a niche rather than a "popular" playground, while C422 has a handful of faithful users (which is a pity, as I find these systems to generally be a breeze to hack…), C621 even less and we may be down to two or three users with C621A hacks; no one has yet cracked W790 or C741. You commend some respect for willing to address such requirements on a Hackintosh rather than jumping to Linux like everybody else… But I submit that for this amount of RAM you should look straight at WRX90 (Threadripper Pro 7000WX) and its 8 RAM channels (up to 2 TB) rather than at TRX50 and its mere 4 channels (1 TB). (If you're willing to go for older DDR4 systems, dual Xeon Scalable can take up to 4 TB RAM with 3DS LRDIMM or Optane DCPMM.)

- 284 replies

-

- amd vanilla patches

- amd kernel patches

- (and 2 more)

-

Please define "popular" in this context… The need for high RAM and/or many PCIe lanes are also addressed by Xeon Scalable/Xeon W-3000, some of which are natively supported by macOS, and which do not raise issues about application compatibility, contrary to Ryzen/Threadripper. I would not say that C621(A) hacks are "popular" by any reasonable acception of the term: We are a handful with these.

- 284 replies

-

- amd vanilla patches

- amd kernel patches

- (and 2 more)

-

I did it by hand. To simplify, I begin by temporarily commenting out the Operation CPVS declaration, so that all further references to its objects show up as errors and then track them one by one: Find one, jump to the corresponding object in the tree in MaciASL left panel, go to the next object to find the closing bracket, delete it, go back to the opening section and complete the deletion, check, rinse and repeat. It's somewhat tedious, and not made easier by the many warnings produced when recompiling the base DSDT. (AMD ACPI tables are an awful mess compared with those from Intel systems.) The new inner conditional statements are worse, as they can be quite long, which makes it difficult to find the closing bracket. But it's maybe not necessary to remove these. Anyway, if the patches by @corpghost keep working these are a much, much, better way to go forward.

-

@kosmos Here are two patched DSDT you may try. The first one follows strictly the method in the first post; 'patched2' then further removes conditional statements on G002 and G001 inside declarations. @Lorys89, please have a look into this. patched.zip

-

Have you tried ACPI patches in OpenCore instead? This is getting naughty, as I now see conditional statements inside declarations, in addition to conditionational statements wrapping full declarations.

-

On AM5, security updates in BIOS also brought some breaking changes in DSDT; maybe similar issues are at play here? Have you tried to compare ACPI tables from the older and nwer BIOS, or re-checked memory whitelisting?

- 3,995 replies

-

- 1

-

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)