iosengineer

Members-

Posts

9 -

Joined

-

Last visited

Recent Profile Visitors

The recent visitors block is disabled and is not being shown to other users.

iosengineer's Achievements

Junior Member (1/3)

3

Reputation

-

trx40 [Discussion] - TRX40 Bare Metal - Vanilla Patches

iosengineer replied to fabiosun's topic in General

Technical question on MMIO whitelist: If I'm willing to spend 4GB (or even more!) RAM to earn the capability to reconfigure my PCIe topology without boot failures, is there a way to configure the MMIO whitelist to instruct macOS to stay away from all memory addresses that are likely to be mapped as PCIe BARs? I have an evolving set of needs from my system, and combined with the Gigabyte D4 error, mean that I need to move PCIe devices around fairly regularly. This seems to work fine on my Intel Hacks, and since I have plenty of RAM in the TRX40, it would be a huge win to just write off a larger chunk of memory to have this flexibility.- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

trx40 [Discussion] - TRX40 Bare Metal - Vanilla Patches

iosengineer replied to fabiosun's topic in General

Thanks @meina222! I am now up and running, including good performance and my custom SAS driver .kexts working :). Main remaining hurdle, after solving the Lightroom issue, is that shutdown results in the machine restarting just after it cuts main ATX power. Thank you @Ploddles (a vote of confidence!!) for providing these rather intense patches for the Lightroom crash! While they didn't initially run on Mojave, installing zsh through Homebrew did allow them to run cleanly. They do indeed work with Camera Raw 13.0 and LR 10 (the latest versions of both). I wonder if there's any interest in this community in a collaboratively-edited guide, on a wiki or through submissions to the Dortania guide? The wealth of knowledge here is pretty amazing.- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

trx40 [Discussion] - TRX40 Bare Metal - Vanilla Patches

iosengineer replied to fabiosun's topic in General

I managed to get my MMIO whitelist populated, and sure enough, it’s allowed NVRAM operations like setting startup disk/last 2 minutes of the installer to succeed. However, iMessage activation failed. I can grab my EFI a bit later, but are there any special considerations with TRX40? I used a fresh SMBIOS and a fresh install, so there should be no contamination whatsoever. I have only one wired Ethernet exposed, correctly en0, no WiFi or anything. It’s even an Acquantia 107, and using a Vega56 with iMacPro1,1 SMBIOS!!- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

trx40 [Discussion] - TRX40 Bare Metal - Vanilla Patches

iosengineer replied to fabiosun's topic in General

Yes, it boots fine with all 3 disabled. I have a potentially-interesting finding for you, @Ploddles & @fabiosun: First off, I was able to boot with Ploddles' config! Woo-hoo, it's undoubtedly an improvement over my minimally-guide-adapted fork of one of my Intel configs, lol (I'm glad to never use it again). Interestingly though, I tried from the start with these three options disabled (AvoidRuntimeDefrag, RebuildAppleMemoryMap, SyncRuntimePermissions), and it did not boot successfully. It did get farther than the ultra-early failure I was seeing before [the Err(0xE) one], but fails on the trusty x86_validate_topology! I have not yet isolated which of the three flags is required to solve this (running out of time for tonight). Additionally, I've read the excellent iGPU tutorial on MMIO Whitelisting—a true community service, thank you @iGPU! I hope your recovery has been brisk and total. That said, even though I like running OpenCore DEBUG and have the boot logs at hand, I've been changing the PCIe config of the machine almost every day this week. In the next couple days, I'll finalize the configuration and MMIO is my top priority before anything else TRX40-Hackintosh-related. Thanks again for the amazing community spirit that all of you are bringing to this forum!- 3,995 replies

-

- 1

-

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

trx40 [Discussion] - TRX40 Bare Metal - Vanilla Patches

iosengineer replied to fabiosun's topic in General

Fascinating — thank you so much @meina222 for your time sharing these details. The Above 4G discussion is interesting, as: I've had it on (both in general, and recommended by Dortania guide) I just tried disabling it, and it actually causes fail-to-boot on my crappy barebones MMIO-less config (it boots again after enabling Above 4G!) I haven't tried Above 4G disabled with your config, but may wait until I have an hour or two and validate MMIO (out of respect for all of your time). Not sure how I got an old copy! I'm 90% sure I'd downloaded it from your post just a couple days ago, but I could have made an error. While I've expressed some degree of hastiness, the last thing I want is to be another...ahem, "Clover-type" user...who doesn't care about the details. I'd been away from Hackintosh since 2006 (I had a rockin' build, lol). It was specifically OpenCore, and its rigorous first-principles-based philosophy, which I discovered almost exactly a year ago and motivated each of the C246 / W480 / TRX40 (mostly Proxmox) builds. So I apologize for any hesitancy to dive into MMIO, but especially now that I understand that it's expected for NVRAM to be broken without that memory mapping—that gives me enough confidence that I'm relatively close and it's worth the time. That said it might take me a couple days, just due to a couple life / work things going on, but I'll report back ASAP. Additionally, I'll be actively following all the posts here for the forseeable future, and deeply appreciate every one of you for your thoughtful engagement with the community! Meanwhile, one project today has been "fabricating" custom copper heatsinks for my 2x 380GB Optane 905p's, which are being used as the special vdev (in mirror) for both my 4x 970 Evo Plus "working" ZFs pool, and 16x SAS3 HDD main ZFS pool. I need to make a big cut to the large one tomorrow. The controllers are not at the same z-height, and I'd like to take my router bit to it for a monoblock fit, but found the small 20mm x 20mm ones can keep the controllers plenty cool with modest airflow. Over 9W in an M.2 form factor isn't the best idea!- 3,995 replies

-

- 1

-

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

trx40 [Discussion] - TRX40 Bare Metal - Vanilla Patches

iosengineer replied to fabiosun's topic in General

Thank you so much @fabiosun for the reference, and also for the correspondence a few weeks back on pve-edge-kernel! (I'm appleguy on GitHub, from this issue) Regarding SIP & NVRAM, the main issue I have with my currently-booting / basic Dortania configs (no MMIO whitelist or custom SSDTs yet) is that booting into Recovery and using csrutil disable causes the machine to hang. csr-active-config in config.plist doesn't seem to have any effect on my machine (I've tried the clear NVRAM option / also reset CMOS and reconfigured BIOS manually). If there's an incremental change I can make to my basic config (linked just above here) to successfully disable SIP for Mojave and Catalina, that would very likely be enough for me to commit to switching over from my W480 to the TRX40 as my primary Hackintosh — and investing in a perfect configuration. I'll try to start the process of tuning an ideal configuration in parallel, but having an SIP disabled state for my simple config (or getting one of the other TRX40 Designare configs to boot) would be very encouraging, as the learning curve on TRX40 is understandably much steeper than any of the Intel configs I've done!- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

trx40 [Discussion] - TRX40 Bare Metal - Vanilla Patches

iosengineer replied to fabiosun's topic in General

@meina222 — Yes, I can share my working config and the slightly-tweaked version of yours (it's nearly identical besides removing the RX 5700XT and disabling SSDTs). ACPI folder is identical to yours, but again most of the SSDTs are disabled in an attempt to get past the early boot failure (this seemed like a long shot since I believe they are used a bit later in the boot process, after the EC-related console messages). Apologies I didn't share this sooner, I'll try to be more on top of things! As for BIOS versions, I also greatly prefer the Titan Ridge to be in Slot 4 (other cards are starved for cooling, and indeed the wiring becomes very challenging). D4 rears its head all the time in PCIe configurations I would like to run, so in a way I'm excited about the F4H BIOS. That said, I can reconfigure things enough with risers to get it to work with either one, so I'll go with whichever BIOS allows me to collaborate best here — that may be F4i in the future, but for now the improvements you've made to the config seem valuable to benefit from. As for MMIO, I'll investigate; it's clearly crucial to TRX40 operation (I haven't learned about it previously, as my Intel hacks have never needed manual MMIO whitelisting). If this is heavily dependent on PCIe configuration (as I'd imagine it is), that's probably the difference. What I don't understand is why my basic Dortania config works without a whitelist! config-sanitized-meina222.plist.zip config-sanitized-iosengineer-booting-dortania-basic.plist.zip ACPI.zip- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

trx40 [Discussion] - TRX40 Bare Metal - Vanilla Patches

iosengineer replied to fabiosun's topic in General

Wow, thank you all so much!!! I'm going to dive in today and the next couple (as needed) to see if I can get a working system. If so, my W480 is going to be relegated to gaming :). @meina222 I just tried the F4H BIOS, and do have it POST-ing now, although it did require removing all PCIe cards. Started with error 92 (can't even enter the BIOS); "PCI Bus initialization is started." This changed to error 62; "Installation of the PCH runtime services." after I removed a second GPU... Got it booting to BIOS by removing all cards and adding in a PCIe x1 / GT 710 for basic video. Is there a tradeoff with the F4H BIOS where some configurations won't work, perhaps explaining why the fix didn't make it into mainline? I'll try re-adding devices and see what I can get working. ——— A couple specific questions ——— I've been searching this thread a lot now, and thank you all for the patience (menia222 — your warnings were clear on F4H, my bad for saving the files and forgetting once I got to try the config!) I'm still able to boot off my original Dortania-guide-from-scratch config, on both F4i and now F4H. However, I can't get @menia222's superior config booting... I've added my own PlatformInfo section, and had to add -v to run into early boot failure on [EB|`B:WFDW] Err(0xE), 0 @ LocHB 71B4903C-14EC-42C4-BDC6-CE1449930E49. I see this is encountered by other folks, but nothing TRX40-related... The error persists after disabling most of the custom SSDTs (except for the ones mentioned in the Dortania guide), as well as the RX 5700XT workaround. Any advice on the config sections that could affect early boot, and actually be different between two F4H Designare's? (Mine is Rev 1.0) Is there any reason I'd need to change RebuildAppleMemoryMap and SetupVirtualMap, which are mentioned in other instances of this error? @jncasey once you're at your machine, I would indeed greatly value a copy of your config! I now have BIOS settings saved to USB for both F4H and F4i, so I can go back to F4i easily to try your config. SMBIOS types: I'm curious about the differing opinions in this thread between iMacPro1,1 and MacPro7,1. @meina222 you seem to be one of the main proponents for 7,1; have you seen any benefits to expansion cards or other behaviors? I'm testing with 7,1 for Catalina to get your config to work, but will have to use iMacPro1,1 for Mojave. ——— One interesting note about the Titan Ridge Thunderbolt card on the TRX40 Designare — I have found it is possible to get the extra lanes out of the slot you use for the AIC, using an M.2 carrier board and M.2 -> PCIe or M.2 -> SFF-8643 / U.2 risers. This works in BOTH the x8 slots (running x4x4) and also the x16 slots (x4x4x4x4), but it is required that the AIC be in the first x4 position. By contrast, none of the other M.2 slots on the board can be used with the AIC (through the riser), so the BIOS must be checking each slot's first x4 lanes for the card. The MaxCloudOn riser also works, although not thrilled with the quality of the contacts (they don't look gold plated). Notably the Titan Ridge trick requires straight bifurcation; I've tried multiple brands of PCIe switches, and however the BIOS discovers the card is not able to detect it when attached to a switch (not shocking, I admit, but still useful to know).- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

trx40 [Discussion] - TRX40 Bare Metal - Vanilla Patches

iosengineer replied to fabiosun's topic in General

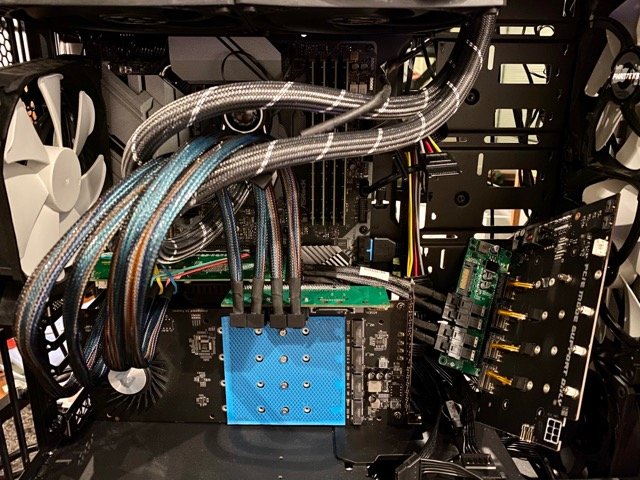

Hey all, and especially @meina222 & @jncasey! (we are all running the TRX40 Designare) Long-time reader, first time poster. I hope to be able to bring a handful of interesting things in return for the amazing community that's gathered here. A few details that might be unique-ish to my setup at the end of this post. I don't need help or support with the odd parts of my setup; in fact my main question (NVRAM) is applicable with nothing installed! My question for all of you — what's the playbook when NVRAM operations like Startup Disk hang the machine? I followed the Dortania guide and was able to get a booting configuration for both Catalina, and Mojave Mojave is ideal focus right now as I'm completing a 180k-asset Aperture migration, but I can handle adaptations between the versions. However, the installer always hung at 2 minutes remaining. I was able to get a working system by finishing the install on my W480. Without NVRAM working, I can't seem to get any of the methods for disabling SIP to work—a requirement for the .kext-based drivers of my ATTO & Highpoint SAS cards, as well as Chelsio 100GbE. I have tried the NVRAM SSDT, but is there any canonical reference that describes this innovation in detail? Information seems tough to find. I did try booting @meina222's config.plist and associated ACPI / .aml's, but wasn't able to get past the Apple logo relatively early in boot. The config may have verbose turned off (mine always leave it on), and tomorrow I'll investigate the logs more. If there is any advice on NVRAM for the Designare, I would be deeply thankful for a tip on which configurations to try. Legacy / LegacySchema (following guides related to using them) did not seem to provide any benefit for me. ——— Designare Resource Allocation Error ——— @meina222 — I had found your discussions on the Gigabyte forum about the ridiculous D4 PCIe resource allocation error, and it is very good to hear that the H bios resolved the issue for you! Indeed outrageous that it's an issue at all, and remains in the latest BIOS... Having just discovered your copy of the H BIOS, I haven't tried it yet; my TRX40 hardware was partially folded into a W480 build, while TRX40 wasn't bootable. I got very far with Proxmox, but a handful of issues were persistent. Still, I'd be interested in comparing notes here at some point! ——— Some fun / unimportant details about my setup + possible areas of experience where I might be helpful ——— Lots of experience with different Optane configs and their compatibility (I have 7x 118GB 800p, 2x 380GB 905p M.2, 1x 280GB 900p AIC, and 1x 960GB 905p U.2) Lots of SAS storage insanity (>140TB / 32+ spindles - mostly SAS, so a lot of macOS SAS experience). Lots of NVMe types, including enterprise (2x 6.4TB Intel P4600, 4x 2TB 970 Evo Plus, 2TB Sabrent Rocket 4.0, 960GB Corsair MP510) Some less-common networking: Chelsio 100GbE cards, Thunderbolt 3 10GbE, QNAP 5GbE, RealTek 2.5GbE, etc Range of AMD GPUs we can test with (Radeon VII, 5700XT, Vega 56, RX 580, W4100, GTX 780; and the sadly-incompatible WX3200). Some really insane PCIe configurations (utilizing the PLX switches that are at the core of "NVMe controllers", to e.g. get x32 usable CPU lanes on a x16-lane Intel platform). Photo of this attached for fun; it is fully operational under macOS with everything populated! Modern Intel HEDT / entry Workstation chipsets (C246 w/ E-2288g, W480 w/ W-1290P). Of course, a TRX40 like you all! (3960x, ECC 4x 3200MHz 128GB, Radeon VII, Gigabyte TRX40 Designare) ...Worked on iPhone 1.0's software :). Honestly though, I am completely serious that I look up to this community with respect and amazement far more than my own career! I wanted to include this before asking a question, just to share my interest in and respect for this community. I genuinely don't intend for it to feel like a "humblebrag" — I do have a lot of hardware, which I offer here in case others are (like me) interested in specific questions about compatibility.- 3,995 replies

-

- 1

-

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)