iGPU

Moderators-

Posts

573 -

Joined

-

Last visited

-

Days Won

17

Content Type

Profiles

Forums

Events

Downloads

Everything posted by iGPU

-

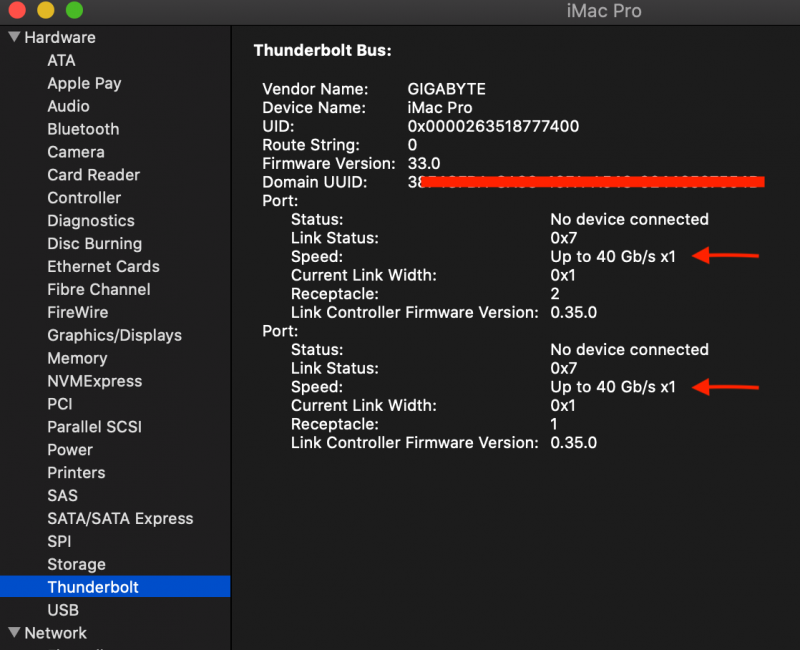

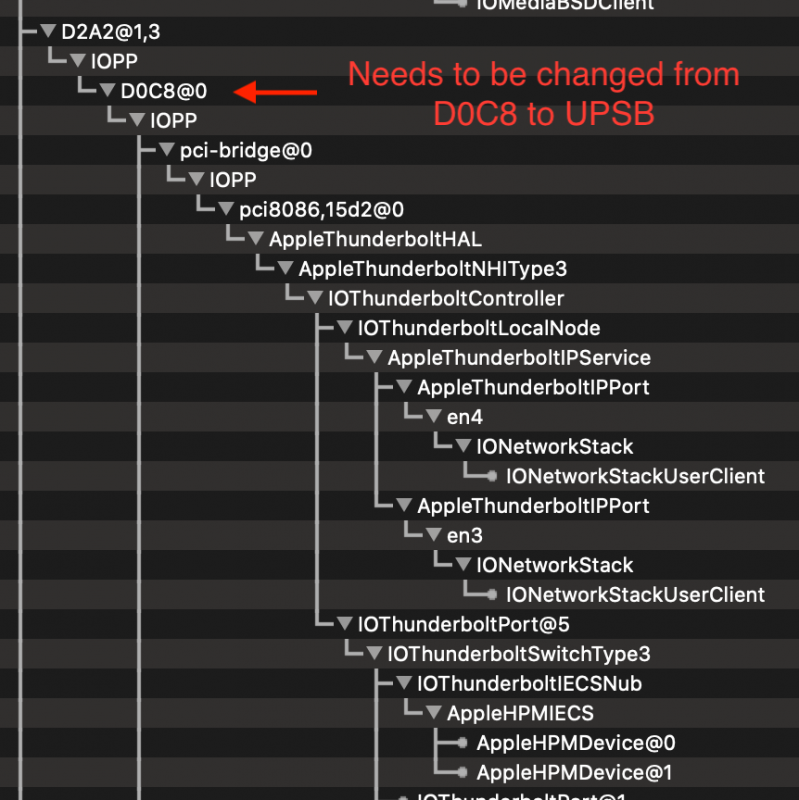

Yes, we won't get full functionality until we get proper SSDT. But with DevProp injection some is better, like the nodes and the speed, which is now 40 GB/c instead of 20. The problem so far with the SSDT is not being able to overwrite D0C8, and this is true for the other SSDTs that are not working: if the device is more nested the SSDT doesn't substitute and doesn't work. The simple ones, like ANS1 and ANS2 do work as these devices are not so nested. I need to study the original DSDT for mobo. These can be made during boot inside OpenCore.

- 3,995 replies

-

- 1

-

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

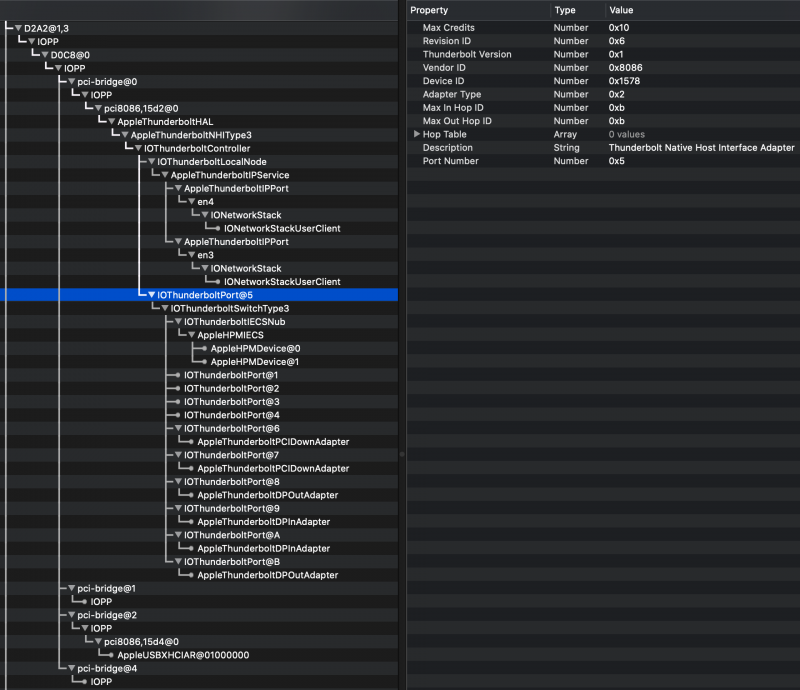

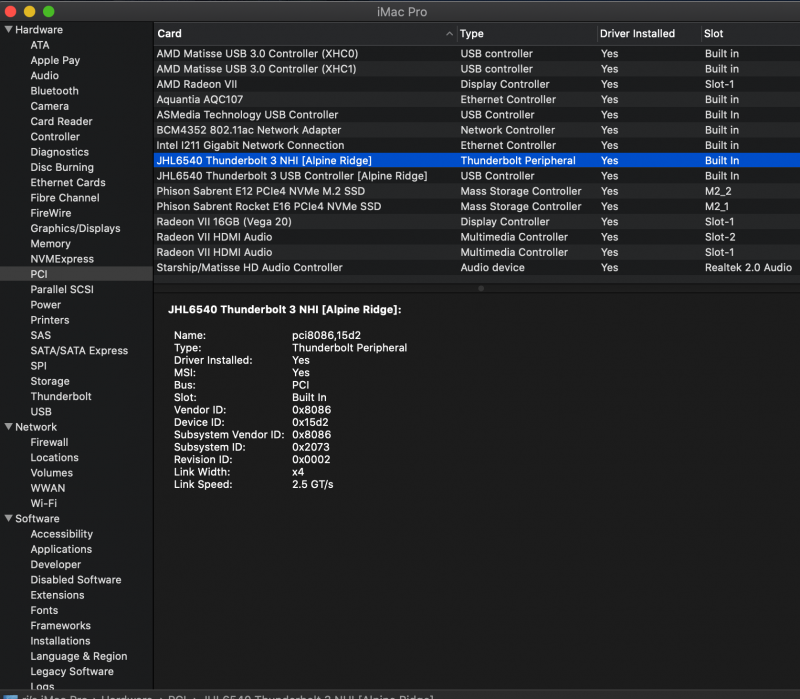

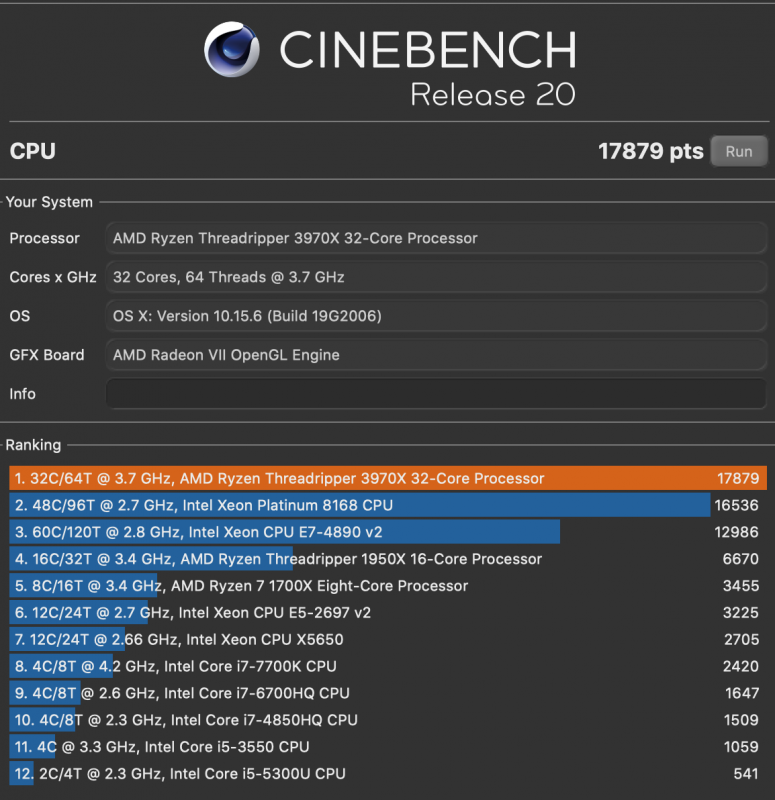

I'll answer your questions in a moment. First I was preparing stop-gap for you using DeviceProperties. Add the parts from attached file and this will inject most properties for TB. I used your exact DROM data. See attachment. If you do you'll see more of following (except your port will be at 7 while my Alpine Ridge is at port 5). Without this our sections at ports 5,7 are empty. This provides better TB functionality. *** The Cinebench was my faster than on VM (max there was ~17,500). The computer boots really fast and is snappier. Dual Radeon VII. This is same as on VM:

- 3,995 replies

-

- 1

-

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

I booted bare metal into Catalina using the above EFI without any problems. Some of the SSDT work. The TB is not injecting properly so more work is needed. It should be fixable. Thanks. It looks similar to mine. I'll work on TB SSDT tomorrow...

- 3,995 replies

-

- 1

-

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

fabiosun, Here are 2 more SSDT based on your IORegistryExplorer file: SBRG and another SATA. Later is only cosmetic.

- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

I saw similar issues with ASRock X570 when TB AIC was in slot 4. I wrote about these issues on the old AMD OSX forum as I studied it quite a bit on the X570 build. In fact, these issues annoyed me so that I left the X570 platform. As for gen 3 or 4, you can set in BIOS to be a fixed gen 3. I seem to recall reading that some people recommended setting BIOS to a fixed gen 3 (not Auto or gen 4) to avoid problems with GPU.

- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

I've dealt with ASUS and GB and feel they're both about the same. I thought ASRock was worse. I've never contacted MSI. But, I've been down this road with the X570, and the problem is similar with the TRX40. The lane sharing issues have to do with these chips (X570 and TRX40), which means it's an AMD problem, not a problem of manufacturer of the motherboard. In my opinion, it's a design flaw by AMD. Instead of lane sharing NVMe with the SATA devices (like Intel), they chose to share NVMe with the PCIe devices.

- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

Do make certain that "SSDT-DTPG.aml" is enabled. I place it first in the ACPI section. It is used by the TB SSDT as well as the SATA and NVMe SSDTs and the GPU SSDTs that I'll upload later.

- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

OK, new v2 SSDT-TB to try. Fist version was not working (in fact, none were working). All other SSDT loaded early today were updated and attached here (there was a typo; mea culpa). Attached here are SSDTs for TB, I211, Aquantia, GFX0 fix, SATA and NVMe drive (the latter are probably specific to fabiosun's build). After running v2, please upload new IORegistryExplorer file. Thanks.

- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

Good: the SSDTs are loading! Can you please post a new IORegistryExplorer file? I'd like to see the effects of the SSDT and look for any adjustments.

- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

Davinci fix. Open attached folder and follow the instructions on the text file, placing the file "libiomp5.dylib" inside the Davinci contents folder. AMD-Davinci-Fix .zip *** Yes, but you'll see more later with proper SSDT... Further, you'll see entries inside USB and Network sections too. And USB speed will be adjusted to maximum with proper SSDT injection.

- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

fabiosun, Here are 2 more SSDT for SATA and ANSI. EDITED: see this link for these two along with 4 other SSDT files. These do inject properties and should show up under SystemInfo/PCI, along with data from the TB SSDTs. BTW, if working, the TB should show up under SystemInfo/Thunderbolt.

- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

Yes, to test for ACPI, run in Terminal: "log show --last boot | grep ACPI" Similarly, to check for TB, run: "log show --last boot | grep Thunderbolt" To check for non-Apple kexts, run: "Kextstat | grep -v com.apple" I will post fix for Davinci later (lunch time at my work). I fixed for X570 which had same issue.

- 3,995 replies

-

- 1

-

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

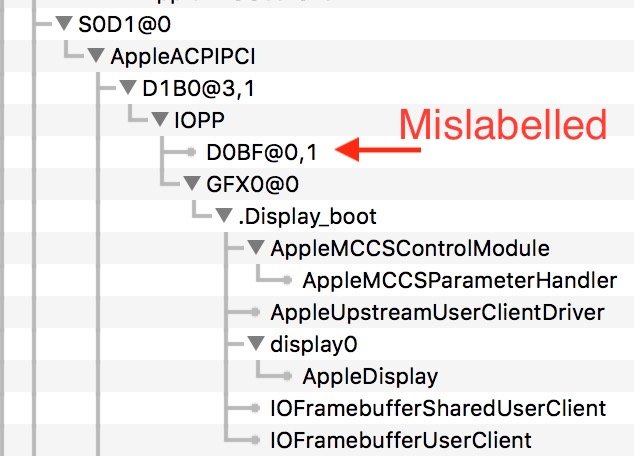

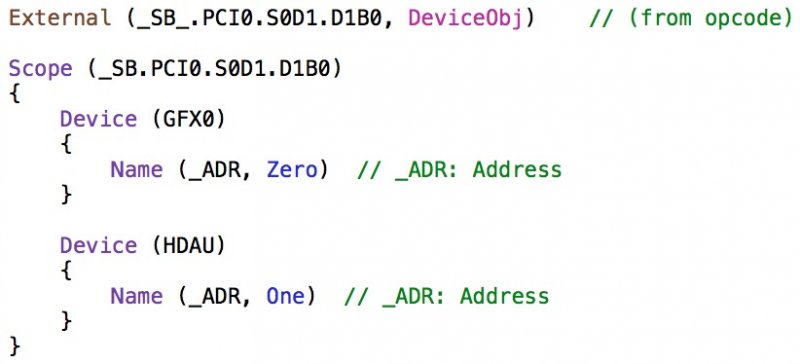

Here are a few SSDTs for fabiosun's mobo. I've attached SSDT for GFX0, Aquantia, I211 (both), and TB. I can make for NVMe later. Note that these simply re-label devices and inject no properties (except TB, which does!). We can later add those items. Attachments were moved; see this link for download of the SSDT files. Correct mislabelled D0BF: Re-name D0BF as HDAU (even though D0BF is at 0,1, 0x01 or One is used):

- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

Post you IORegistryExplorer and I can modify SSDTs (and post a "how to").

- 3,995 replies

-

- 4

-

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

This might work. You'll need to fill-in SN parts. I also left kexts activated for BT/WiFi; turn-off it you don't want them. This is using compilation from yesterday for OC v061. Patches were from fabiosun's post above. *** Depending up whether "Above 4G Encoding" is enabled or disabled, "npci=0x2000" may need to be entered into the boot arg section of OpenCore. If you get a boot failure, try adding "npci=0x2000" and see if that helps. It is not present in the attached EFI folder. *** EDITED 26 Aug: See this post for a better EFI folder that boots Catalina and Big Sur bare metal.

- 3,995 replies

-

- 1

-

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

Interesting. This has similar structure to my old X570 build. I shoud be able to adapt SSDTs from that build for the TRX40 mobo. I'll post later once working. (I'm at work and still need to re-install Catalina before I can test.)

- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

My boot argument not so complicated, but I don't know if it will help your Docker problem:

-

Where did he post? I'd like to try as we share same hardware.

- 3,995 replies

-

- amd vanilla patches

- amd kernel patches

- (and 3 more)

-

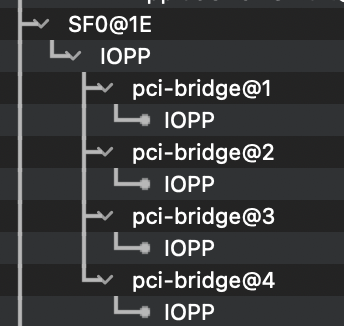

I realize that it's due to lane sharing. (I wrote extensively about this same on the X570 build on the AMD OS X forum and here, section 6.) I wrote about the SF0 issue so that other users can check other mobos for a similar response. I think they will find the same result as this most likely is a function of the TRX40 chip. What I think it might suggest, is a technique to de-populate the SF0 device. In other words, if SF0 is populated, we can simply add NVMe drives (maybe a small one for Proxmox?; small ones are inexpensive) to attempt to move things out of SF0. This will facilitate writing SSDT for the non-SF0 devices.

- 145 replies

-

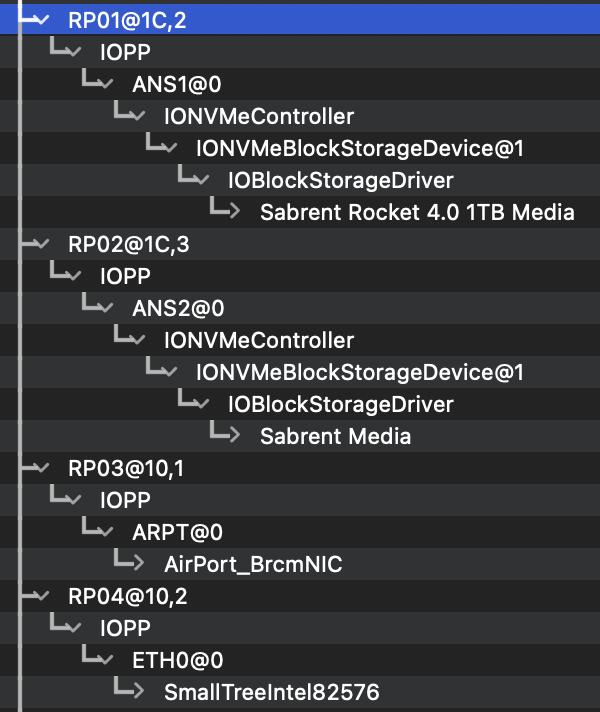

I agree, problem order is: 1. passing bridges in VM 2. rename SF0 But problem #2 varies with mobo and setup. Until I added a 3rd NVMe drive to the MSI mobo, TB was added to SF0 (as were the 2 NVMe drives). However, once I added a 3rd NMVe drive (filling all NVMe slots), all NVMe drives moved out of SF0 into their own devices inside the PCI0 tree. This has now left SF0 un-populated. Now, when I add the TB card, the two parts, while separated into different devices since there is no pci-bridge to bind them, are no longer inside SF0. Instead, these 2 parts are inside the PCI0 tree, leaving them accessible to a simple SSDT (once problem #1 is solved). So there seems to be curious behavior with the SF0 device, depending on number of occupied NVMe slots. NVMe Drives (the 3rd drive contains Win10 and not visible; renaming RP0x done with an SSDT). Un-populated SF0:

- 145 replies

-

- 1

-

-

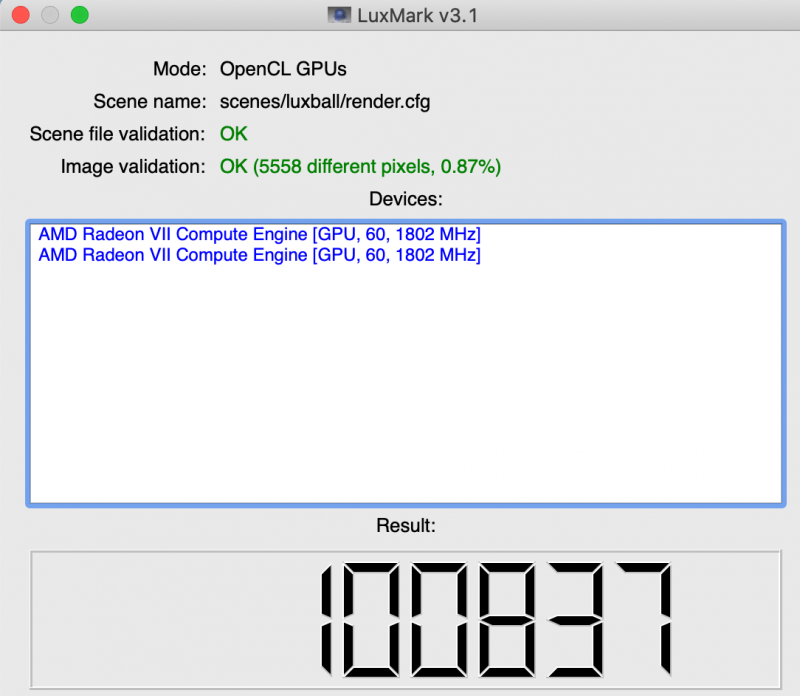

Tonight I ran tests for iMacPro1,1 vs MacPro7,1 for Cinebench 20 and LuxMark. The results were identical all around. I'm sticking with iMacPro1,1.

-

@tsongz, You BT/Wifi card seems a bit wonky. As I mentioned earlier, can you test it in another Hackintosh to prove that it works? If it doesn't work then you can be a new card rather than spend more time trouble-shooting. *** I have many set-ups for SSDT/kext/DevProp for Vega 56, 64, 5700 and Rad VIIs. If you want I can post them. I worked them up for users on the X570 build. If you have an air-cooled Vega 56/64 you want to stay away from the RadeonBoost kext as it will spin up the fans. The SSDTs or DevProp are better for those. Let me know what exactly you want and I'll post it.

-

It's recommended to sign out of iCloud before changing SMBIOS. Then sign back in after the change. You'd want to change serials as it would be a 'different' computer.

-

Don't worry about that warning. I started with that but not necessary. As for kext, you don't need to open, I was simply explaining where it is located. But, do copy EXACTLY what I showed in the image. I'll re-upload below, but as text portion and you can copy and paste into OC config file.